Развитие электроники определяется увеличением производительности и функциональности полупроводниковых технологий. Новые устройства становятся все более сложными, и важными факторами их разработки являются конфигурации выводов компонентов, шаг между ними и плотность компоновки. Также новые устройства используют современные интерфейсы: DDR3, DDR4, PCI Express Gen3, USB 3.0 и другие, для которых необходимы новые типы внедрения в печатную плату. Все это обусловливает постоянно растущий спрос на новые методы корпусирования, увеличивающие плотность межсоединений на печатной плате.

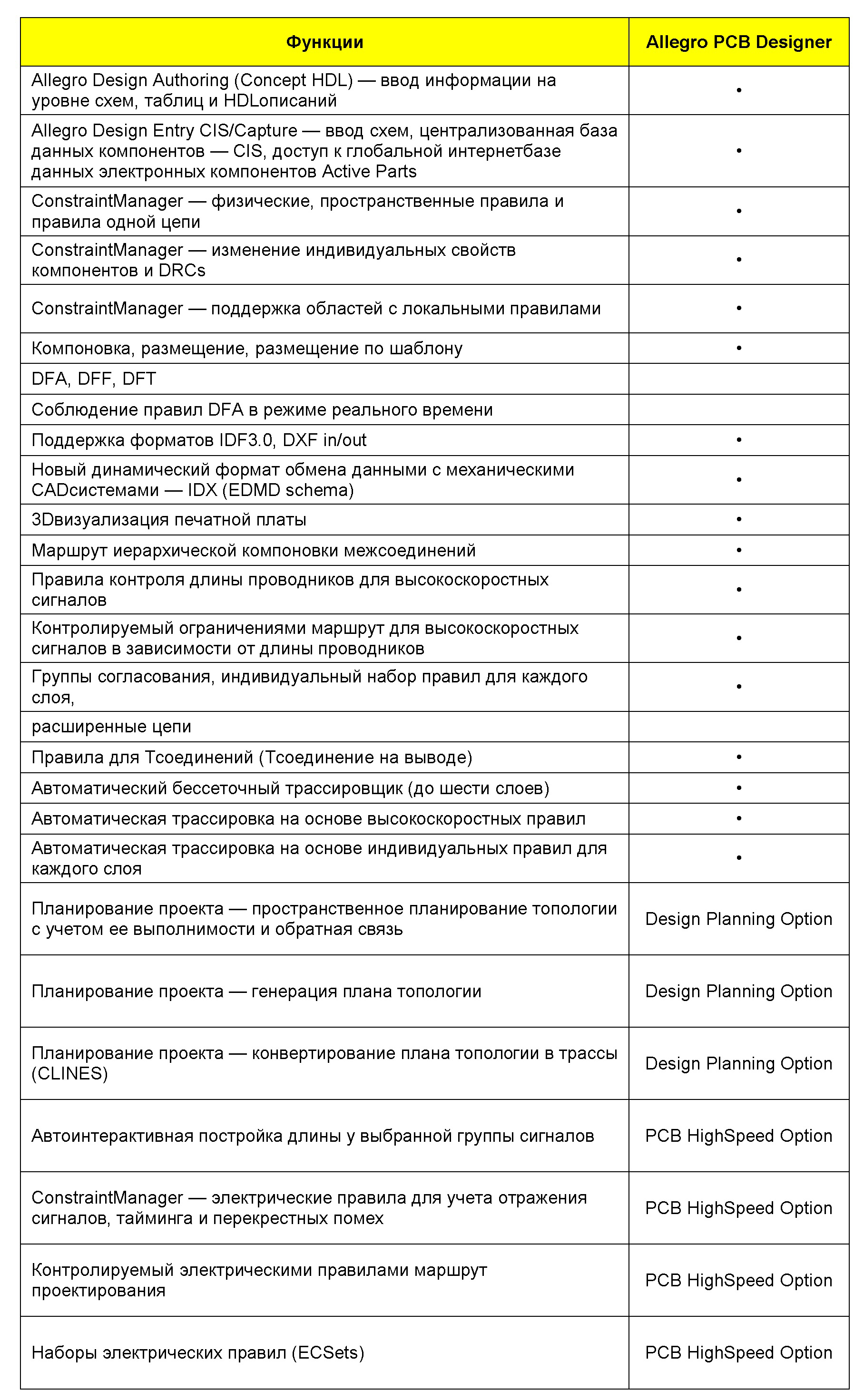

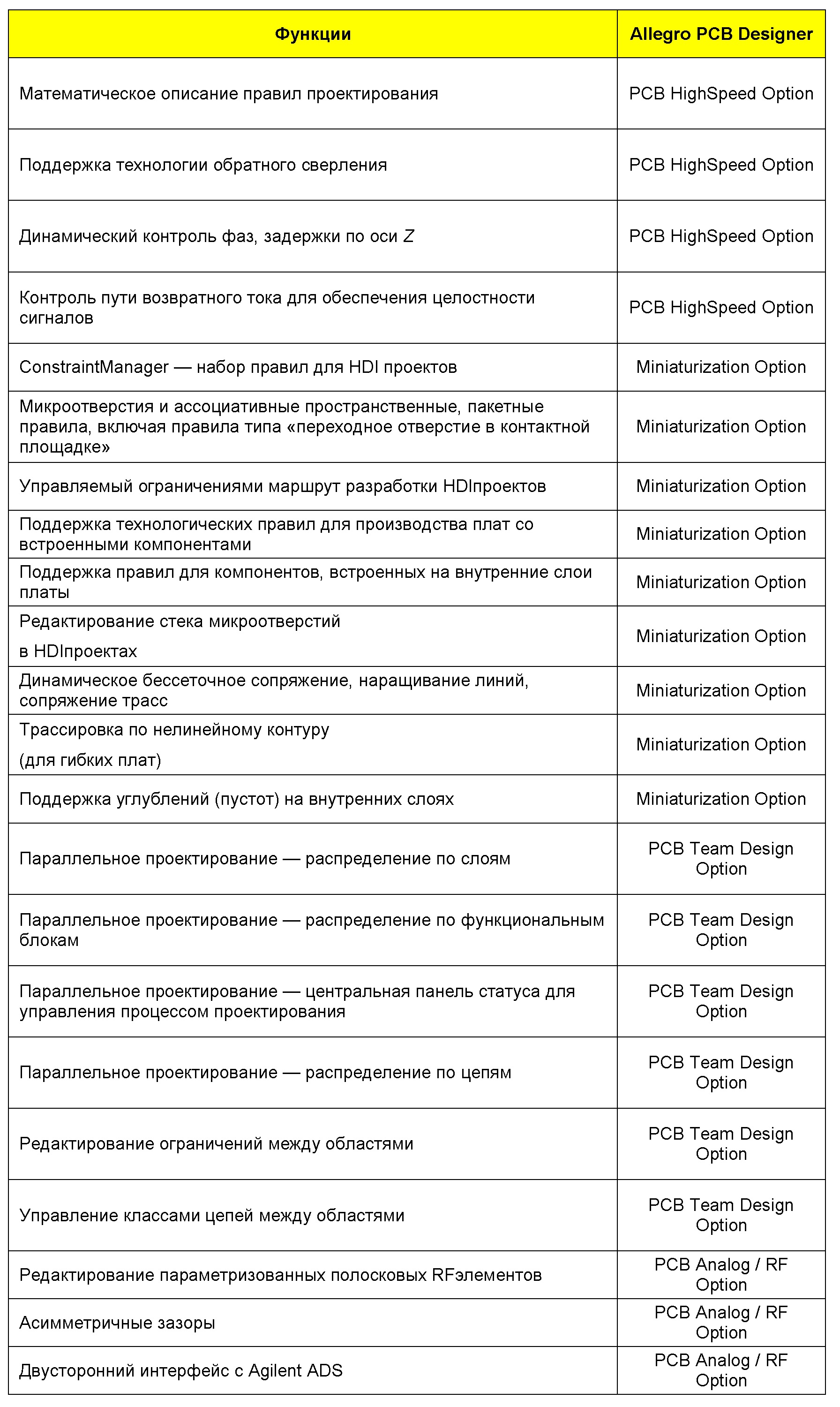

Сегодня для решения столь сложных задач инженерам необходимы современные технологии проектирования систем на уровне печатных плат, которые будут отвечать технологическим и методологическим требованиям. К ним, например, относится пакет программ Cadence Allegro PCB Designer, о некоторых важнейших функциях которого рассказывается в данной публикации.

Планирование соединений и трассировка

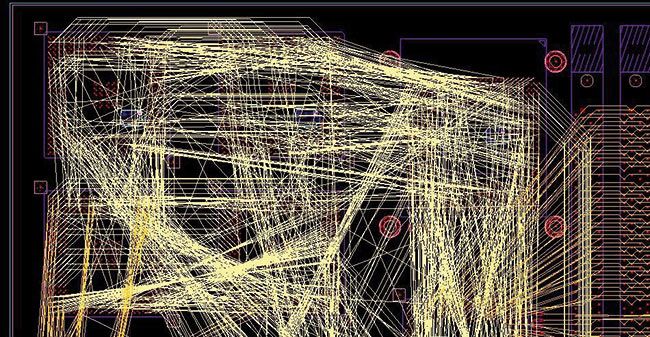

Сложные печатные платы с большим количеством электрических и технологических ограничений, высокой плотностью монтажа компонентов и множеством высокоскоростных сигнальных шин данных требуют при проектировании нового подхода. Использование традиционных и устаревших САПР, таких как PCAD, становится недопустимым, так как они не способны обеспечить готовность подобных проектов в кратчайшие сроки. На первый план выходят САПР, которые активно развиваются и отвечают современным реалиям в электронной промышленности. Cadence Allegro PCB Designer в сочетании с опцией Interconnect Flow Planner содержит уникальную функцию для создания плана соединений и последующего преобразования его в готовую трассировку. Данный механизм планирования и трассировки дает инженеру возможность прокладывать большие массивы сигналов в виде специальных объектов — сигнальных жгутов, что позволяет значительно упростить проектирование и кардинально снизить время на разработку (рис. 1).

Инженер видит на экране не сотни или тысячи пересекающихся линий электрических связей, а план прокладки больших массивов этих связей. Понятно, что такой подход в разы повышает эффективность работы — есть возможность прокладывать сигнальные жгуты между слоями, планировать размещение переходных отверстий, избегать пересечения жгутов друг с другом, вести сигналы по кратчайшему пути и т.д. Для каждого жгута можно задать свой набор свойств, обеспечить его трассируемость с точки зрения временных задержек сигналов в нем, копировать планы трассировки между разными проектами. Allegro PCB Editor на программном уровне «подскажет» разработчику оптимальные пути прокладки жгутов, а затем с помощью уникальных алгоритмов преобразует получившийся план в готовую топологию.

Рис. 1. Технология планирования соединений на плате Allegro Interconnect Flow Planner позволяет пользователям уменьшить число слоев и значительно сократить длительность цикла разработки сложных плат

Ускорение проектирования времязависимых цепей

Все более широкое применение высокоскоростных цифровых интерфейсов, таких как DDR3, DDR4, PCI Express, USB 3.0, налагает целый ряд ограничений, которые должны быть учтены при проектировании печатной платы.

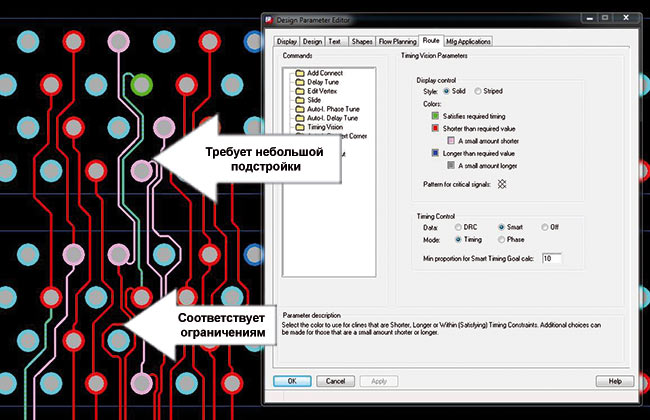

Allegro PCB Designer с опцией HighSpeed помогает эффективно и быстро достичь соответствия требованиям современных интерфейсов. Данная опция расширяет набор контролируемых электрических ограничений, с помощью которых инженер может в кратчайшие сроки добиться максимальной целостности сигналов и обеспечить их точные временные характеристики. Также вместе с опцией HighSpeed в Allegro PCB Designer становятся доступны мощные инструменты управления времязависимыми цепями, такие как Autointeractive Delay Tuning, AutoInteractive Phase Tuning, AutoInteractive Convert Corner, Timing Vision и т.д. Остановимся на некоторых из них более подробно.

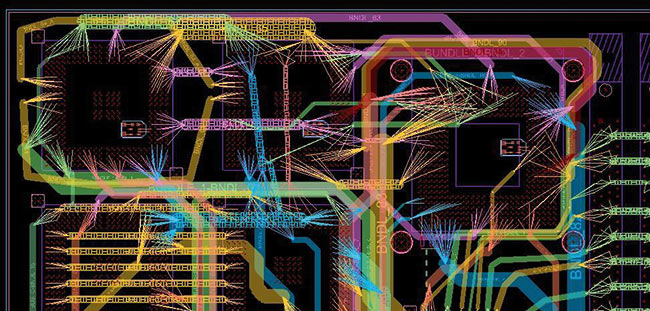

Инструмент Autointeractive Delay Tuning, сокращенно AiDT, дает пользователям возможность быстро подстраивать длину у выбранного набора сигналов на плате, например байтового тракта или полностью всего интерфейса. Этот инструмент кардинально снижает время подстройки временных задержек у большого массива сигналов — с нескольких часов до нескольких минут (рис. 2). Пользователю достаточно обвести рамкой выделения нужный набор сигналов, после чего в соответствии с параметрами, указанными в Constraint Manager, произойдет автоматическая подстройка длины трасс.

Рис. 2. Автоматическая подстройка длины проводников до и после применения нового инструмента Auto-interactive Delay Tuning

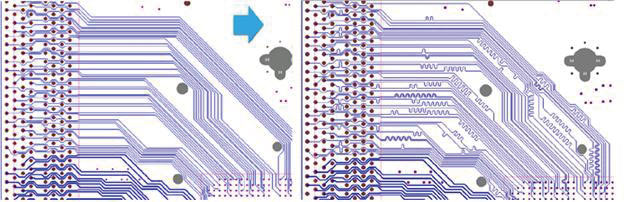

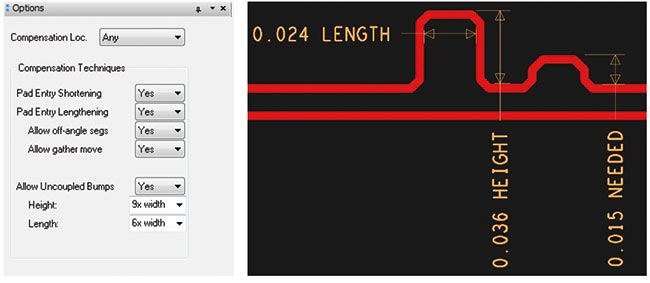

Рис. 3. Инструмент Auto-Interactive Phase Tuning для автоматической подстройки динамической фазы в дифференциальной паре

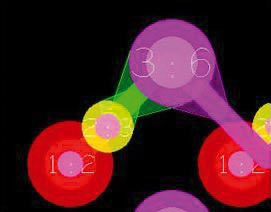

Инструмент AutoInteractive Phase Tuning, сокращенно AiPT, дает возможность в считаные минуты обеспечить оптимальную динамическую фазу для дифференциальной пары. Под динамической фазой подразумевается обеспечение равенства длины проводников с учетом их изгибов на разных участках прокладки от источника к приемнику сигнала. Благодаря данному инструменту значительно сокращается время на выравнивание длин проводников в дифференциальной паре.

Пользователь должен вести непрерывный контроль за времязависимыми цепями на плате. Специально разработанная встроенная в Allegro PCB Editor «среда» визуального контроля Timing Vision позволяет пользователю быстрее находить не соответствующие временным ограничениям трассы на печатной плате. Данный инструмент включает средства цветовой индикации, возможность выбора специального узора для трасс и специальные всплывающие подсказки. В зависимости от заданных временных ограничений в Constraint Manager трассы на плате будут подсвечены разным цветом, который выбирается в настройках (рис. 4).

Рис. 4. Инструмент Timing Vision для визуального контроля за длиной трасс с учетом временной зависимости сигналов

Проектирование с учетом технологий производства

Allegro PCB Editor поддерживает технологии проектирования с учетом тестопригодности (DFT), возможности изготовления (DFF) и технологичности сборки (DFA). Все эти важнейшие ограничения проверяются на этапе разработки топологии наряду с электрическими ограничениями. Пользователи могут выбирать количество тестовых точек и размеры их контактных площадок, определять зоны запрета для размещения тестовых точек и создавать отчеты для проверки степени готовности платы к тестированию. В Allegro PCB Editor включена специальная функция контроля правил DFA в режиме реального времени. С ее помощью можно контролировать и визуально отслеживать на плате любые нарушения, связанные с зазорами между компонентами. При сближении компонентов на максимально допустимое правилами DfA расстояние программа автоматически выдаст предупреждение и «остановит» пользователя перед возможным нарушением правил.

Передача данных на производство

Allegro PCB Designer может генерировать полный набор файлов для производства и тестирования печатной платы, включая Gerber 274x, NC Drill, NC Route и т.д. Но что особенно важно, Cadence поддерживает промышленную тенденцию перехода к «безгерберной» технологии производства с помощью нового универсального формата IPC2581. Особенность данного формата заключается в том, что все данные, необходимые для производства, сборки, сверловки, фрезеровки и тестирования платы, хранятся в одном унифицированном файле. Пользователи могут выбирать данные для файла IPC2581 с целью защиты своей интеллектуальной собственности. Импорт IPC2581 в Allegro PCB Editor позволяет просматривать файл.

Маршрут проектирования плат с технологией HDI

Миниатюризация — сегодня это главный тренд в электронике. Устройства уменьшаются, а их производительность и функциональность растут. В проектах всё чаще применяются микросхемы в BGAкорпусах с шагом выводов от 0,8 мм и менее, что требует применения технологии повышенной плотности межсоединений (HDI) для вывода сигналов на внутренние слои от площадок BGA с помощью фэнаутов. Конструкция платы в этом случае требует применения микропереходных отверстий, размещения ПО на контактных площадках, особых технологических процессов в изготовлении. Все это должно учитываться системой проектирования печатных плат в полном объеме на уровне контроля правил проектирования.

Allegro PCB Designer в сочетании с опцией миниатюризации (Miniaturization Option) позволяет создавать проекты на основе технологии HDI любой степени сложности. Сюда включены следующие возможности:

- работа с микроотверстиями;

- оптимизация смешанных переходных отверстий;

- контроль слепых и глухих отверстий на слое;

- контроль этажерок переходных площадок;

- контроль ступенчатого расположения переходов;

- площадка внутри площадки;

- массовое изготовление переходов;

- контроль на соответствие технологии изготовления;

- учет правил проектирования HDI при автоматической трассировке.

В Allegro PCB Designer в сочетании с опцией миниатюризации включается множество различных инструментов интерактивной трассировки, таких как расталкивание слепых и глухих отверстий, динамическое сопряжение микропереходов, поддержка встроенных компонентов, трассировка по контуру для гибкожестких плат и многое другое (рис. 5).

Рис. 5. Динамическое сопряжение контактных площадок и проводников при интерактивной трассировке значительно экономит время на этапе подготовки проекта к производству

Поддержка технологии встроенных компонентов

Уменьшение размеров конечного изделия может быть достигнуто различными путями. Один из них состоит в размещении корпусных элементов на внутренних слоях платы. Allegro PCB Designer при наличии опции миниатюризации предлагает технологию трассировки, управляемой ограничениями для встроенных компонентов. Она поддерживает как традиционные технологии прямого и непрямого присоединения, так и новейшие технологии двустороннего подключения для одного компонента, вертикальное расположение компонента, встроенные компоненты для двусторонней платы. Опция миниатюризации позволяет пользователю создавать углубления и управлять ими на слоях, выделенных под размещение встроенных компонентов.

Создание аналоговых ВЧ и СВЧплат

Пакет Allegro PCB Designer вместе с опцией проектирования аналоговых радиочастотных цепей Analog/RF Design представляет собой среду разработки для смешанных сигналов — от создания схемы до планирования с сохранением истории изменений, — обеспечивающую повышение производительности процесса проектирования радиочастотных изделий до 50%. Эта опция позволяет инженерам создавать, объединять и дорабатывать аналоговые радиочастотные и микрополосковые схемы совместно с цифровыми и аналоговыми схемами в среде Allegro PCB Designer. Имея развитые возможности планирования и мощные интерфейсы со средствами численного моделирования в радиочастотном диапазоне, эта опция дает инженерам возможность начинать процесс проектирования радиочастотных схем из Allegro Design Authoring, Allegro PCB Designer или Agilent ADS.

Параллельная коллективная разработка

Для сокращения длительности цикла разработки все чаще организуются географически разнесенные коллективы разработчиков. Традиционно применяемые при коллективной разработке процедуры ручной проверки и доводки очень медленны, времязатратны и связаны с риском внесения ошибок.

Технология Allegro PCB Design Partitioning реализует многопользовательскую параллельную методологию разработки для ускорения процесса и уменьшения времени планирования. С ее помощью множество разработчиков могут трудиться одновременно, имея доступ к общей базе данных независимо от удаленности. Разработчики могут разделять процесс проектирования на ряд задач или областей, для которых будет производиться планирование и редактирование, и поручать их нескольким членам коллектива. Разработки могут разделяться вертикально (секции) с программно задаваемыми границами или горизонтально (слои). В результате каждый разработчик может видеть все отдельные секции, наблюдать за процессом создания конструкции и оценивать результаты других проектировщиков. Возможность такого разделения помогает значительно уменьшить длительность циклов разработки и ускорить процесс проектирования.

Технология автоматической трассировки печатных плат

Технологии трассировки печатных плат тесно связаны с редактором печатных плат PCB editor. Посредством интерфейса трассировщика PCB Router вся конструкторская информация и ограничивающие условия автоматически поступают из PCB editor. По окончании трассировки вся информация автоматически передается обратно в PCB editor.

Возросшая сложность разработок, плотность размещения и наличие дополнительных ограничивающих условий для высокоскоростных схем делают процесс ручной трассировки трудным и времязатратным. Для решения задач трассировки сложных соединений требуется мощная автоматизированная технология. Надежный и испытанный в производстве автоматический трассировщик имеет режим пакетной трассировки с расширенным управлением стратегией трассировки и встроенными стратегиями трассировки.

Автоматическая трассировка с учетом правил DFM

Средство оптимизации для производства (Design For Manufacturing, DFM), входящее в трассировщик Allegro PCB Router, значительно уменьшает число впоследствии отбраковываемых изделий. Его алгоритмы обеспечивают возможность автоматического разнесения проводников с использованием всего имеющегося свободного места. Автоматическое разнесение проводников помогает повысить технологичность путем перемещения проводников для дополнительного увеличения зазоров между проводниками и выводами, между проводниками и контактными SMDплощадками и освобождения дополнительного места для проводящих полигонов. Пользователи используют преимущества гибкости задания допусков вручную либо по умолчанию.

Во время трассировки могут быть заданы свободные углы и контрольные точки. Алгоритмы DFM автоматически делают оптимальные отступы, начиная с наибольших и уменьшая их в доступных пределах. Средство создания контрольных точек автоматически вставляет на плате тестовые переходные отверстия или контактные площадки. Контрольные точки в виде тестовых переходных отверстий могут располагаться как на лицевой, так и на обратной стороне платы, что позволяет использовать односторонние или двусторонние тестеры. У разработчиков есть возможность выбора методологии вставки контрольных точек, соответствующей их производственным требованиям. Контрольные точки могут быть фиксированными во избежание необходимости модификации тестовой оснастки. Ограничивающие условия для контрольных точек включают форму поверхности тестовых зондов, размеры переходных отверстий, сеток и минимальные расстояния между центрами отверстий.

Автоматическая трассировка, управляемая ограничениями для быстродействующих плат

Высокоскоростные ограничивающие условия и алгоритмы трассировки прменяют дифференциальные пары, сетевое планирование, временные параметры сигналов, уровень перекрестных помех, трассировку набора слоев и специальные требования к геометрии, предъявляемые к современным высокоскоростным цепям. Алгоритмы автоматической трассировки аккуратно выполняют трассировку с использованием переходных отверстий и вблизи них, а также автоматически поддерживают соответствие заданным временным или пространственным критериям. Автоматическое сетевое планирование применяется для снижения уровня шума в чувствительных к нему цепях. К различным областям платы можно применять свои правила проектирования, например можно задать правило максимально плотного размещения в области проводников и менее строгие правила на остальной части платы.

Разработка высокоскоростной электроники должна быть обеспечена адекватными программными и аппаратными средствами проектирования. Allegro PCB Designer — это мощный инструмент в руках профессионала, занимающегося разработкой современной быстродействующей электроники. Последнее обновление — Update Release № 2, вышедшее в марте этого года, включает большое количество новых инструментов работы, которые частично были описаны в данной статье.

Понравилась статья? Тогда поддержите нас, поделитесь с друзьями и заглядывайте по рекламным ссылкам!